## Physical Fault Injection and Side-Channel Attacks on Mobile Devices: A Comprehensive Analysis

Carlton Shepherd<sup>a,\*\*</sup>, Konstantinos Markantonakis<sup>a,\*</sup>, Nico van Heijningen<sup>b</sup>, Driss Aboulkassimi<sup>c</sup>, Clément Gaine<sup>c</sup>, Thibaut Heckmann<sup>d,e,f</sup> and David Naccache<sup>d,f</sup>

#### ARTICLE INFO

Keywords: Fault Injection Attacks Side-channel Attacks System-on-Chips (SoCs) Mobile Device Security Embedded Systems Security

#### ABSTRACT

Today's mobile devices contain densely packaged system-on-chips (SoCs) with multi-core, high-frequency CPUs and complex pipelines. In parallel, sophisticated SoC-assisted security mechanisms have become commonplace for protecting device data, such as trusted execution environments, full-disk and file-based encryption. Both advancements have dramatically complicated the use of conventional physical attacks, requiring the development of specialised attacks. In this survey, we consolidate recent developments in physical fault injections and side-channel attacks on modern mobile devices. In total, we comprehensively survey over 50 fault injection and side-channel attack papers published between 2009–2021. We evaluate the prevailing methods, compare existing attacks using a common set of criteria, identify several challenges and shortcomings, and suggest future directions of research.

#### 1. Introduction

Powerful personal mobile devices have become ubiquitous over the past decade, which is coupled with a substantial decline in the use of personal computers [152]. Estimates show that 3.8 billion people worldwide will be active smartphone users in 2021 [151]. 84% of US citizens use a smartphone regularly, rising to 96% in the 18–29 year old category, while 52% also use a tablet device [121]. Mobile devices are used widely for security- and privacy-sensitive applications, including banking, instant messaging, navigation, social media, corporate email, and accessing cloud-based media. Consequently, device data is often of major interest to malicious adversaries and forensic investigators.

In certain scenarios, these actors may resort to physical attacks to circumvent existing software and hardware security mechanisms on mobile devices, such as trusted execution environments (TEEs), full-disk and file-based encryption, and secure boot procedures. In this work, we analyse two well-known classes of physical attacks—fault injections and side-channel attacks—and their application to mobile devices. Such attacks are well-understood in the smart card and secure element (SE) domain [104, 67, 128, 82]. Indeed, they are usually employed during the evaluation of smart cards and SEs under the Common Criteria framework [98].

Fault injection attacks (FIAs) perturb the device's physical conditions beyond that which it was intended; for exam-

carlton.shepherd@rhul.ac.uk (C. Shepherd); k.markantonakis@rhul.ac.uk (K. Markantonakis) ORCID(s): 0000-0002-7366-9034 (C. Shepherd) ple, using intense electromagnetic (EM) pulses, high ambient temperatures, and under- and over-volting the device's supply voltage. These attacks can induce errors in internal electronic components, which can be utilised to recover cryptographic keys and other secret data. In contrast, physical side-channel attacks (SCAs) exploit physical measurements produced by the device during execution. Particular side-effects, like EM emissions and power consumption, may expose secret information if the side-effect is dependent on the data being executed.

Unfortunately, the complexity of today's mobile devices has frustrated the application of traditional FIAs and SCAs used historically against simpler platforms, such as microcontroller units (MCUs). Modern mobile system-on-chips (SoCs) employ high-frequency (1GHz+), multi-core CPUs with multi-stage pipelines and instruction-level parallelism; contain mixed analog and digital components; and are used to host complex operating systems (OSs) with various concurrent and virtualised processes. These aspects complicate the acquisition of side-channel measurements and the precise and accurate injection of faults. Ultimately, this has changed the types of physical attacks that have found success in the current literature.

In this work, we consolidate and extensively evaluate the state of the art in physical fault injection and side-channel attacks on mobile devices. In total, over 50 research papers are examined from 2009 to 2021, which are compared using the attack goals, prerequisites, target platforms, and reported results. From this work, we identify some significant challenges and limitations, and highlight potential future research directions. To the best of our knowledge, we present the first comprehensive survey in the area with respect to modern mobile devices.

<sup>&</sup>lt;sup>a</sup>Information Security Group, Royal Holloway, University of London, Egham, Surrey, United Kingdom

<sup>&</sup>lt;sup>b</sup>Netherlands Forensic Institute, The Netherlands

<sup>&</sup>lt;sup>c</sup>Equipe Commune CEA Tech – Mines Saint-Etienne, CEA Tech, Centre CMP, Gardanne, France

<sup>&</sup>lt;sup>d</sup>French National Gendarmerie Research Center (CREOGN), France

<sup>&</sup>lt;sup>e</sup>Institut de Recherche Criminelle de la Gendarmerie Nationale, France

fÉcole Normale Supérieure, Paris, France

Part of this work was presented to the European Commission during the EU Horizon 2020 EXFILES project (No. 88315) [43].

<sup>\*</sup>Corresponding author

<sup>\*\*</sup>Principal corresponding author

**Table 1**Summary of related surveys.

| Work                         | Year | Summary                                                                           |

|------------------------------|------|-----------------------------------------------------------------------------------|

| Barenghi et al. [25]         | 2012 | Fault injection attacks on cryptographic systems.                                 |

| Shepherd et al. [144]        | 2016 | Security properties of secure execution platforms and TEEs for embedded systems.  |

| Fournaris et al. [46]        | 2017 | Micro-architectural attacks for embedded systems.                                 |

| Spreitzer et al. [148]       | 2017 | Network, micro-architectural, software, and some hardware SCAs on mobile devices. |

| Mirzargar & Stojilović [110] | 2019 | Physical SCAs and covert channels for FPGAs and cryptographic ASICs.              |

| Sayakkara et al. [135]       | 2019 | Electromagnetic side-channel analysis of embedded systems.                        |

| Han et al. [68]              | 2019 | Program analysis using side-channel analysis for embedded systems.                |

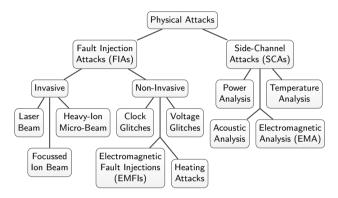

Figure 1: Taxonomic scope of this survey.

## 1.1. Scope

This study examines *physical* fault injection and sidechannel attacks on SoC-based mobile devices that physically observe (SCAs) or perturb (FIAs) their execution, whether wholly or in part. In this context, mobile SoCs are defined as the primary integrated circuit (IC) for supporting a multitasking OS, e.g. Android, on a commercially available mobile platform. The SoC incorporates a single- or multi-core CPU with memory management unit (MMU) support; multiple memory modules, e.g. dynamic and non-volatile RAM, and flash storage; external peripheral interfaces, e.g. interintegrated circuit (I2C); and, optionally, a dedicated GPU.

The taxonomic scope of this paper is shown in Figure 1. Wholly software attacks are outside the scope of this survey, which include but are not limited to: micro-architectural attacks exploitable only in software, such as cache timings and side effects of speculative execution, and software timing attacks on security protocols and cryptosystems. Along with alternative hardware attack vectors, such as NAND mirroring [146] and hardware trojans [154], these topics constitute significant distinct research areas that justify separate analyses.

While the focus of our work is physical FIAs and SCAs on mobile SoCs, references from the embedded systems literature are examined as supporting material where appropriate. This is particularly the case where a fault injection or side-channel attack has recently compromised a related evaluation target, like an Internet of Things (IoT) SoC, which may inspire future attacks on mobile devices.

## 1.2. Related Surveys

In prior work, Barenghi et al. [25] (2012) presented a review of FIAs against symmetric and asymmetric cryptosystems on general computing systems. We note that this work precedes the proliferation of modern mobile SoCs and their associated security mechanisms, e.g. TEEs and full-disk encryption. In 2016, Shepherd et al. [144] reviewed secure and trusted execution environments for IoT systems, comparing their security features and briefly discussing their susceptibility to physical attacks. No FIAs or SCAs were analysed in detail, however. Spreitzer et al. [148] (2017) surveyed general SCAs on mobile devices, covering physical attacks at a high level, alongside network traffic analysis, cache timings, and other software channels outside the scope of this work. Fournaris et al. [46] (2017) focussed on X86 and ARM Rowhammer attacks, with a brief discussion of electromagnetic analysis (EMA). In 2019, Mirzargar and Stojilović [110] surveyed SCAs on field-programmable gate arrays (FPGAs) and application-specific ICs (ASICs). The use of power, electromagnetic, and thermal side-channels were examined for creating covert channels. Sayakkara et al. [135] (2019) presented a tutorial on using EMA for digital forensics. Methods are described for EMA measurement acquisition, their analysis for hardware and software profiling, and the related standards; it is unrelated to attacks on mobile security mechanisms. Han et al. [68] (2019) presented a tutorial of program analysis using EMA and power analysis. The work provided a description of methods for signal acquisition and their statistical analysis using correlation analysis and machine learning.

These works are summarised in Table 1. Additionally, other studies have surveyed general mobile attacks [168], cryptographic analysis methods [31], and attacks on simpler security devices, e.g. smart cards [104]. However, no survey paper has extensively covered state-of-the-art physical fault injection and side-channel attacks on modern mobile devices. This paper addresses that gap.

#### 1.3. Structure

We begin in §2 with background information on mobile SoCs, their high-level system features, and their use in common hardware-assisted security mechanisms. Following this, comprehensive surveys of physical fault injection and side-channel attacks are presented in §3 and §4 respectively. The surveyed works are extensively compared in §5,

where several shortcomings, challenges, and potential future research directions arising from existing work are identified. Finally, §6 concludes this paper.

## 2. Background

This section provides background information for understanding recent fault injection and side-channel attacks. In summary, we provide an overview of mobile SoCs and widely deployed hardware-assisted security mechanisms, including TEEs, secure boot, key management systems, and full-disk and file-based encryption.

#### 2.1. Mobile System-on-Chips (SoCs)

System-on-chips—ICs with the core components for establishing a working computing system—have become the centrepiece of contemporary mobile hardware due to their reduced energy efficiency and physical footprint. Silicon vendors typically design SoCs through the configuration of reusable semiconductor intellectual property (IP) blocks developed in-house or licensed from a third party, like ARM. Vendors integrate varying numbers of such components according to their specifications, which are fabricated as interconnected subsystems onto a single IC using specialised buses for data transfer and control. High-frequency multicore CPUs with multi-level cache hierarchies and MMUs are at the foundation of today's application processors, e.g. ARM's Cortex-A73 [18]. Supporting on-SoC components include diverse memory units, e.g. dynamic RAM, flash storage and read-only memory; timers and real-time clocks; security extensions and cryptographic accelerators, e.g. ARM TrustZone and CryptoCell [17]; integrated GPUs and audio digital signal processing (DSP) units; and input/output (I/O) interfaces for communicating with sensor hubs, input devices, and other off-SoC peripherals.

The exact capabilities of mobile SoCs varies between silicon vendors. At the time of publication, ARM-based SoC designs are used in approximately 90% of mobile handsets, tablets, and IoT devices [150]. The Qualcomm Snapdragon, HiSilicon Kirin, Samsung Exynos, Apple A, and the MediaTek Helios series are some widely used ARM-based SoCs used by mobile original equipment manufacturers (OEMs).

#### 2.2. Trusted Execution Environments (TEEs)

A TEE is an isolated, parallel execution environment that aims to protect sensitive code and data from privileged software attacks. TEEs have gained widespread use on mobile devices for preserving user authentication algorithms, cryptographic keys, digital rights management systems, and payment processing applications. At present, ARM TrustZone and the GlobalPlatform TEE—a suite of specifications governing the use of TEEs—are the main enablers on mobile devices, arising from their compatibility with the ARM architecture [13, 41, 144]. Intel Software Guard Extensions (SGX) and the AMD Platform Security Processor (PSP) are two alternative TEE systems for Intel and AMD chipsets; however, these are independent technologies on predominantly non-mobile platforms, e.g. servers and workstations.

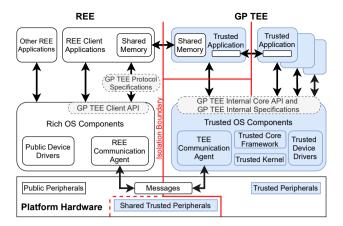

Figure 2: GlobalPlatform TEE system architecture [54].

## 2.2.1. GlobalPlatform TEE Specifications

The GlobalPlatform TEE (GP TEE) is a suite of specifications for defining the architecture, management and security requirements of a TEE [54, 57, 58]. It divides execution into two worlds: the rich execution environment (REE, or the *untrusted* or *non-secure* world) and the TEE (*trusted* or *secure* world), as shown in Figure 2. The REE includes the mobile's native OS, its firmware and its user applications, whereas the TEE contains a separate trusted OS with a security kernel, device drivers for security-critical peripherals, and a set of lower-privileged trusted applications (TAs). Each world must execute with hardware-enforced isolation if they utilise the same underlying hardware platform. This to impede privileged REE software adversaries from compromising the control flow, memory regions and peripheral devices of the secure world.

For inter-world communication, REE applications may access the TEE using a tightly controlled interface at the platform's highest privilege level or, alternatively, using a shared memory view created by the TEE. The GlobalPlatform Client API [52] standardises the communication interfaces through which REE applications can invoke TEE TA functions and transmit/receive data, including supported data types and response codes. The Internal Core API [55] specifies functions through which TAs can access services provided by the trusted OS, such as sources of time, external peripherals, cryptographic functions, and secure storage media. Additionally, the Secure Element [59], Sockets [60] and Trusted User Interface [53] APIs have also been specified for enabling TAs to access hardware secure elements, networking services, and user interface devices respectively. For the full specifications, the reader is referred to the GlobalPlatform Technology Document Library [56].

The GP TEE Protection Profile (PP) characterises the security definitions and requirements for evaluating a target of evaluation (TOE) under the Common Criteria (CC) framework. It addresses "threats to the TEE assets that arise during the end-usage phase and can be achieved by software means...focuses on non destructive software attacks that can be easily widespread...and constitute a privileged vector for

getting undue access to TEE assets without damaging the device itself" [58]. At a minimum, it stipulates that TEEs should defend against two high-level adversary types:

- Basic remote attacker: "Performs the attack on a remotely controlled device or alternatively makes a downloadable tool that is very convenient to end-users. The attacker retrieves details of the vulnerability identified in the identification phase and [...] makes a remote tool or malware and uses techniques such as phishing to have it downloaded and executed by a victim [into the untrusted world]."

- Basic on-device attacker: "Has physical access to the target device; it is the end-user or someone on his behalf. The attacker is able to retrieve exploit code, guidelines written on the internet on how to perform the attack, and downloads and uses tools to jailbreak, root, reflash the device in order to get privileged access to the REE allowing the execution of the exploit. The attacker may be a layman or have some level of expertise but the attacks do not require any specific equipment." [58].

The TEE OS and TAs are deemed trusted software components; security issues within either can compromise the services that the TEE aims to provide. From a hardware perspective, the GP TEE should have access to a secure clock, entropy source, and volatile and non-volatile memory. The GP TEE must also be initialised from a root of trust (RoT) using a secure boot process to ensure authenticity. How this is implemented in practice is both platform- and architecture-specific. We describe this process for ARM TrustZone in §2.3, the main method by which GP TEEs are instantiated on ARM-based mobile SoCs. Crucially, however, the TEE's initialisation process must be performed without trusting or co-operating with the REE. In general, the GP TEE must operate self-sufficiently without depending on any untrusted components in the REE [54, 58].

GlobalPlatform-compliant TEEs must satisfy Common Criteria Evaluation Assurance Level 2 (EAL2) as a minimum baseline. In general, TOEs that meet this level provide 'low-to-moderate' security assurances under the CC grading framework and is satisfied through evidence of structured testing [163]. This is lower than smart cards and secure elements, which are usually evaluated to CC EAL4+ thereby providing 'moderate-to-high' security assurances. EAL4+demands a higher degree of security testing rigour, requiring methodical design, testing and review in addition to the requirements of lower EALs.

It is important to consider that smart cards and secure elements often consider physical attackers with access to specialised testing equipment, such as high-end oscilloscopes, chemical workbenches, and electromagnetic pulse apparatus [162]. These threats are beyond the minimum protection scope of GlobalPlatform-compliant TEEs. This lack of

coverage means that physical fault injection and side-channel attacks can offer a potential avenue for subverting GP TEE implementations.

#### 2.2.2. ARM TrustZone

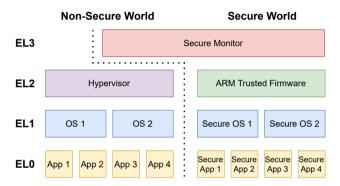

ARM TrustZone is a set of extensions to the ARM architecture for creating a secure world of execution. It is the main implementation for providing the hardware-enforced separation required by GlobalPlatform-compliant TEEs on ARM-based devices [13, 41, 144]. Similarly, TrustZone partitions the execution platform into 'secure' and 'non-secure' worlds. Each world hosts its own OS and applications at different processor exception levels, which communicate over a secure monitor at the highest ARM exception level (EL3), as shown in Figure 3. Secure monitor mode is entered into using the ARM Secure Monitor Call (SMC) interface, which handles the world context switch. A reference implementation of the secure monitor code and bootloading process is provided by the Trusted Firmware project [95], which manufacturers may tailor to their own SoCs.

Figure 3: The ARM v8.4-A exception model [15].

A control signal, the 'non-secure' (NS) bit, is used by TrustZone-enabled SoCs to store the current world of execution. The NS-bit is propagated through all areas of the SoC where adversaries may attempt to access secure world material, including page tables, cache lines, and bus transactions to memory firewalls and peripheral controllers. Unauthorised access attempts to secure world-only resources are prevented by on-SoC controllers that are configured at boottime. As specific examples, the TrustZone Peripheral Controller (TZPC) prevents non-secure accesses to secure world-only peripheral interfaces, and the TrustZone Address Space Controller (TZASC) can be used to prevent non-secure accesses to secure world memory addresses.

At its core, TrustZone is a SoC security architecture; it does not provide the software components for realising a complete TEE containing a hardened security kernel, support for multiple TAs, and so on. To bridge this gap, numerous TrustZone-based TEE implementations have been developed commercially, e.g. Huawei's iTrustee [76], Samsung's TEEGRIS [133], Trustonic's Kinibi [161], and the Qualcomm TEE [127], many of which conform to the GlobalPlatform TEE specifications. Lastly, we note that Trust-Zone aims primarily to defend against privileged non-secure

<sup>&</sup>lt;sup>1</sup>It is still possible that GlobalPlatform TEE implementations may contain countermeasures against advanced physical attacks beyond the minimum compliance requirements.

world software attacks. Hardware threats are outside of its protection scope; if such attacks are considered reasonable, ARM's SecurCore smart card may be used with a TrustZone-enabled SoC to protect the relevant assets [14].

## 2.2.3. Apple Secure Enclave

The Secure Enclave is an independent subsystem on Apple SoCs (from the Apple A7 [9]) for protecting content even when the application processor is compromised. Detailed technical data is not publicly available besides high-level features described in the Apple security documentation [9, 87, 11] and outcomes from independent reverse engineering efforts [102, 40]. From the available information, the Secure Enclave comprises a hardware co-processor—the Secure Enclave Processor (SEP)—a true random number generator (TRNG); a unique root key for implmenting devicespecific key binding; an I2C controller for secure storage to external non-volatile memory (NVRAM); and a public key accelerator (PKA). The Secure Enclave manages cryptographic operations for Apple iOS, including file-based encryption, and user data for the Touch ID and Face ID biometric systems [9].

The SEP is a physically separated processor that runs a security kernel—sepOS, an Apple fork of the L4 micro-kernel—which is initialised during the secure boot process. This separation offers inherent resistance to certain classes of side-channel analysis from software adversaries on the application processor, e.g. cache timing attacks. The confidentiality of run-time Secure Enclave data is protected using a Memory Protection Engine, which encrypts memory blocks using AES in XEX (xor-encrypt-xor) mode and computes cipher-based message authentication code (CMAC) tags that are both stored in external untrusted DRAM.

The PKA is used to secure public-key cryptographic operations, namely key generation (i.e. from the root SEP key), encryption and decryption, and digital signature services using RSA and elliptic curve cryptography (ECC). Undisclosed countermeasures are implemented to resist power analysis attacks, including differential power analysis (DPA). Besides this, a separate AES memory encryption engine, located in the DMA path between the application processor and NAND flash memory, is used for file-based encryption—discussed in §2.5—the keys for which are managed by the Secure Enclave. From the Apple A9 SoC series, undisclosed countermeasures are also utilised by this module to thwart power analysis attacks. Related to this, the Secure Enclave contains monitoring circuits to enforce the intended operating voltage and clock frequency against fault injection attacks [10].

## 2.2.4. Google Titan M

In 2017, Google announced the Titan M for the Pixel 2 smartphone, a mobile hardware security module that executes independently of the application SoC [63]. Similar to the Apple Secure Enclave, it is also largely undocumented. From what is known, the Titan contains flash memory, CPU, RAM and a TRNG in a single package designed to resist physical side-channel analysis, including power and elec-

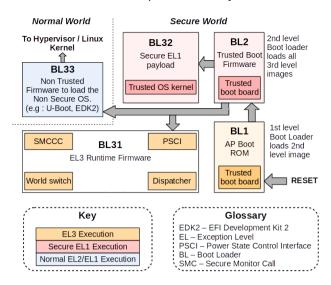

Figure 4: Generic ARM boot procedure [16, 169].

tromagnetic analysis, and voltage-, clock- and temperature-based fault attacks. The Titan M supports general key management and cryptographic operations using the StrongBox KeyStore APIs (§2.4) and is used for flash memory encryption/decryption. In addition, the Titan stores the last known safe Android version during legitimate device updates. This is referenced by the Pixel's secure boot process for preventing rollback attacks to vulnerable OS versions.

#### 2.3. Secure Boot

Adversaries with the ability to load unauthorised boot-loaders and secure/non-secure world binaries may trivially disable critical security mechanisms. Consequently, secure boot procedures have been deployed for cryptographically enforcing the use of authorised software components at boot-time. Mobile devices contain multiple bootloader stages of increasing complexity and decreasing security privilege; a generic boot procedure is shown in Figure 4. At the beginning, code within on-SoC ROM (BL1) is used to perform basic SoC setup operations, e.g. power-on self-test (POST) and clock initialisation, after receiving a reset signal. The trusted world binary and secure monitor firmware (BL2) are subsequently authenticated and loaded thereafter. Importantly, this is done *before* loading the non-secure world image containing the native OS and its applications (BL3).

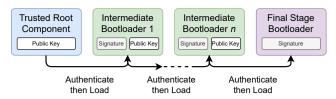

For authenticating each component, a common method involves verifying a sequence of digital signatures from the initialisation ROM, which is inherently trusted. The ROM contains a public key certificate—a hash of which may reside in one-time programmable (OTP) eFuses—for verifying the signature of the second bootloader. Upon successful verification, this bootloader is loaded, which itself contains a public key for verifying and loading the following bootloader. The process is repeated until the non-secure world image is eventually loaded and executed (Figure 5).

Boot images are signed under a private OEM signing key; if any unauthorised components are introduced, the sig-

Figure 5: High-level authenticated secure boot process.

nature verification check will fail and the boot sequence terminated. Some devices also contain OTP eFuses that are permanently set ('blown') after failed checks, thus signalling that device assets may have been compromised [134]. Details are scarce about the exact cryptographic algorithms used by OEMs, although the ARM Trusted Board Boot requirements specify SHA-256 and RSA-2048 or 256-bit ECDSA for bootloader signatures [16].

#### 2.4. Secure Storage and Key Management

TEEs may utilise one of two methods for secure persistent data storage: 1), encrypting data using keys accessible only to the TEE; and, 2), directly storing data to an external device over a trusted path. To support the first case, TEE implementations usually possess their own key hierarchies rooted in a device-specific hardware unique key (HUK) from which descendent keys are generated using a key derivation function (KDF). These keys may then be used by TAs and the TEE OS to encrypt arbitrary binary data, including other cryptographic keys, whether generated within the TEE or sent from the REE. This provides a notion of device 'binding' where data cannot be transferred and decrypted on another device with its own HUK. GP TEEs support a variety of standard cryptographic algorithms, such as 128/192/256bit AES in various modes of operation, e.g. CBC, XTS, and CTR; up to 2048-bit RSA; 160- to 521-bit ECC (ECDSA and ECDH); and 128- or 196-bit triple DES. The Internal Core API [55] specifies a full list of supported algorithms and modes of operation.

At present, regular application developers are not given direct access to TEEs. OEMs have, however, developed key management systems for providing abstracted access to TEEbased cryptography services. On Android devices, the Keymaster service exposes API functions for generating, using and containerising cryptographic keys in the TEE from user applications [7]. Key material is generated within the TEE and is never exposed to the calling application. Developers are purposefully not given access to these keys; instead, they indirectly use this material by calling abstracted encryption, decryption, and signature verification and signing functions available through the Android framework. Where supported, the StrongBox Keymaster serves as a TEE substitute for addressing physical attacks, which implements the Keymaster in a mobile hardware security module, e.g. the Titan M [65] (§2.2.4).

On Apple devices, the SEP (§2.2.3) is manufactured with a hardware-based unique ID (UID) from which cryptographic keys are derived for device binding. These keys are never exposed to the main application processor. The SEP handles key management for secure boot signature verification, securely storing biometric data at rest, and general OS cryptographic operations. For the latter, additional keys are derived from a user-inputted password and a hardware secret, which are used for per-file and volume encryption [9].

#### 2.5. Full-Disk and File-Based Encryption

Full-disk encryption (FDE) encrypts all user data on a device at a block level using symmetric key encryption, usually AES. Throughout standard device usage, data is continuously encrypted before it is written to a flash storage device that exposes itself as blocked memory; during read operations, the data is decrypted before returning it to the parent process. Android's FDE implementation is based on the dm-crypt Linux kernel module, which encrypts data using a device disk encryption key (DEK) with 128-bit AES in CBC mode. The DEK is encrypted by a key encryption key (KEK) derived from the user's PIN or password, both of which are managed within the TEE. Only if the user successfully passes an authentication challenge are the keys released; failing this, neither the KEK nor the DEK are unlocked, thereby preventing data decryption [6].

File-based encryption (FBE) encrypts data at a filesystem level, unlike FDE that operates at a block or volume level. FBE is generally considered to be FDE's successor on mobile devices: it permits essential data to still be used for critical device functions—accessibility services, emergency calls, and alarm managers—while keeping sensitive data encrypted when the device is locked [8]. Commonly, FBE generates unique AES file encryption keys (FEKs) for dynamically encrypting and decrypting user files, e.g. documents, as they are written to and read from a persistent storage device. FBE is used by Secure Enclave-enabled Apple devices, which manages keys within the Apple SEP. In contrast, Android devices (version 7.0+) support directory-level encryption using keys managed in the Keymaster TEE TA or a mobile hardware security module.

## 3. Fault Injection Attacks

Fault injection attacks (FIAs) are active attacks that physically perturb the device beyond its intended operating conditions. This can induce abnormal system behaviour for uncovering secret data under execution or accessing restricted code regions and functionality. FIAs have a long-standing history and have been analysed in great depth in the wider literature, particularly for smart cards and other embedded MCUs [25, 5, 30, 174, 21, 119, 72].

FIAs are categorised as *transient vs. permanent*, and *invasive vs. non-invasive*. Transient faults are temporary errors that are recoverable following a system reset or cessation of the fault source. Their aim is to (temporarily) disrupt the program control flow or corrupt the results of an instruction to gain unauthorised access to sensitive code and data. While having the same end goal, permanent faults indefinitely alter the state of target components, the effects of which persist irrespective of device restarts and resets.

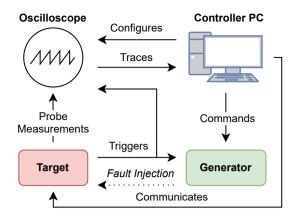

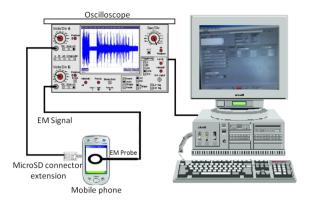

**Figure 6:** Generic FIA and SCA setup. For FIAs, the generator injects the fault after receiving the trigger; for SCAs, the trigger activates the measurement process.

A typical physical FI (and SCA) setup is shown in Figure 6. The investigator instruments the device under test (DUT) to activate an external generator at run-time following a hardware- or software-based trigger. The generator perturbs the DUT with a precisely timed and calibrated fault using the desired method; for example, an EM burst over a particular SoC die location or a momentarily high voltage at the DUT's power supply.<sup>2</sup> The investigator uses a control computer to analyse the resulting outputs—register values, memory address contents, encryption/decryption results, oscilloscope traces, etc.—in order to discover useful faults, such as instruction corruption and decryption errors.

## 3.1. Invasive FIAs

Invasive FIAs involve significant alteration to the DUT, whether during the attack's preparation or execution. Relevant preparation techniques include depackaging the SoC or IC and removing any protective layers (decapsulation) to directly induce faults into its internal components. These processes risk irreparable damage or destruction of the target under evaluation, potentially leading to permanent data loss. At the execution stage, the application of high-energy visible light and ultraviolet pulses, near-infrared lasers, and focussed ion beams may be used to flip the transistor states of memory cells and other components [147, 165, 124, 136, 159, 92, 167]. Such methods have been historically successful against simpler systems [82, 25, 165], but have found limited utility against mobile SoCs from publicly available information.

## 3.1.1. Ion-based FIAs

The costliest FIAs employ focussed ion beams (FIB)—typically liquid metal ion sources, e.g. gallium ions—and heavy-ion microbeams (HIMs) that operate with extreme precision (~2.5nm). In the semiconductor industry, FIB workstations permit the manipulation of IC silicon substrates *in*

situ, potentially enabling hardware-level reworking (microsurgery) of security-critical components and the reading of hardware-fused keys. In 2009, Torrance and James [159] used FIBs to perform IC microsurgery for reading encryption keys from an application-specific IC (ASIC) implementation of the DES cipher. In comparison, HIMs ionise IC semiconductor material with high-energy radiation to induce single-event upsets (SEUs) in digital logic systems. This was leveraged by Li et al. [92] (2015) to trigger exploitable decryption faults in an RSA implementation on an SRAM FPGA. The FPGA was irradiated using 1 GeV of carbon ions that generated decryption bit errors at a rate of 8 times per hour. The authors theorise that 1024-bit private key recovery can be achieved after ~128 hours, but experimental results were not given. FIB and HIM attacks impose substantial cost (\$100,000+ USD) and require access to specialised expertise and testing equipment. No such attacks have been publicly disclosed against mobile SoCs to date.

## 3.1.2. Laser FIAs

Laser FIAs target ICs with intense sources of visible, infrared or ultraviolet light with the aim of inducing SEUs. In 2017, Vasselle et al. [167] presented the results of a laser FIA that bypassed the secure boot process of an undisclosed Android smartphone with an ARM Cortex A9-based (1.4GHz) SoC. This was achieved following physical and software reverse engineering, package decapsulation, and targeting the SoC with a 978nm infrared laser. The authors could modify the Secure Configuration Register (SCR) containing the TrustZone NS-bit with 95% accuracy (see §2.2.2) in order to access secure world assets during non-secure execution.

Beyond mobile SoCs, Colombier et al. [37] (2019) described laser FIAs for modifying the bits of words fetched from flash memory on a ChipWhisperer board with a 32-bit ARM Cortex-M3 (7.4MHz). The MCU was decapsulated before applying a 3W infrared laser (1,064 nm), which generated faults that modified movw ARM instructions to movt.<sup>3</sup> Using these errors, 128-bit AES key recovery was possible from a reference AES software implementation after 128 attempts and two faulty ciphertexts. Additionally, the faults were also used to bypass the authentication check of a mock PIN verification algorithm.

## 3.2. Non-Invasive FIAs

Non-invasive FIAs require little-to-no tampering of the DUT, e.g. SoC/IC decapsulation, removing adjacent components, and the use of corrosive chemicals. With reasonable care, their effects usually disappear after removing the stimulus or resetting the device. As a rule of thumb, such attacks can be conducted using lower cost, commercially available equipment and risk significantly less damage than their invasive counterparts [25]. Four well-studied classes of fault injection attacks fall into this category:

#### • Voltage-based glitch attacks: Under- or over-volt the

<sup>&</sup>lt;sup>2</sup>Instrumenting device triggers is a significant challenge in black-box environments, rendering accurate and precisely calibrated fault injections more difficult than white-box testing.

<sup>&</sup>lt;sup>3</sup>The movw instruction moves the least significant 16 bits of an immediate integer value into a target register's lowest 16 bits, while movt moves the *most* significant bits to a register's *upper* 16 bits.

| Technique      | Precision (Space) | Precision (Time) | Cost      | Skill     | Damage Risk |

|----------------|-------------------|------------------|-----------|-----------|-------------|

| Voltage Glitch | Low               | Moderate         | Low       | Moderate  | Low         |

| EMFI           | Moderate          | Moderate         | Moderate  | Moderate  | Low         |

| Clock Glitch   | Low               | High             | Low       | Moderate  | Moderate    |

| Heating        | Low               | Low              | Low       | Low       | Moderate    |

| Light Pulse    | Moderate          | Moderate         | Moderate  | High      | Moderate    |

| Laser Beam     | High              | High             | High      | High      | High        |

| FIB            | Very High         | Very High        | Very High | Very High | High        |

| HIM            | Very High         | Very High        | Highest   | High      | High        |

Table 2

Summary of FIAs based on [25] and [92].

EMFI: Electromagnetic FI, FIB: Focussed ion beam, HIM: Heavy-ion micro-beam.

device's power supply beyond its intended operating limits [125, 24, 156, 158, 157, 23, 115] (§3.2.1).

- Clock glitches: Increase or decrease the device's clock frequency used to synchronise the operation of internal components [29, 2, 153, 85] (§3.2.2).

- **Heating attacks**: Expose the DUT to temperatures beyond its maximum or minimum guidelines [86, 88, 66] (§3.2.3).

- Electromagnetic FIs (EMFIs): Expose DUT components to targeted, high-energy EM pulses [39, 129, 42] (§3.2.4).

Table 3.2 presents a summary of FIAs and their temporal and spacial precision, relative complexity, and damage risk.

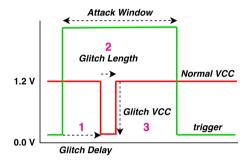

#### 3.2.1. Voltage-based Glitch Attacks

Voltage glitches manipulate the target's supply voltage. An attacker can generate single- or multi-bit faults by underor over-volting this source or redirecting it to ground to generate brownouts. This can corrupt the contents of memory units or coerce microprocessors into misinterpreting and even skipping program instructions. In existing literature, such effects have been used to skip security-critical checks, e.g. digital signature verification; bypass system-level access control features; and to recover information about cryptographic key material under execution.

One of the first voltage glitches against a mobile phone SoC was presented by Barenghi et al. [23] (2009), who targeted a reference software RSA implementation on a 32-bit ARM9 CPU (ARM926EJ-S).<sup>4</sup> The work exploited errors in energy-intensive load instructions after the target was provided a low supply voltage (underfeeding). During instruction fetches, the authors could change the binary encoding of logical operations (AND to EOR), conditional additions (ADDNE to ADDEQ), and conditional branches (BNE to BEQ). These errors were used in three attacks against OpenSSL v0.9.1i: 1), for RSA factorisation when using the Chinese remainder theorem (CRT); 2), an e-th root attack for recovering an input

Figure 7: Voltage FIA parameters [156].

message encrypted under a correct and faulted encryption procedure; and 3), a theoretical attack for secret key recovery during message signing. For the first, 6.6%–39% RSA-CRT computations could be faulted of which 3.0%–39% were exploitable, while, for the second, 36.42%–62.77% of 1,000 faulted instances were useful. The instruction swaps occurred only a small number of times, which "may be reduced up to a single one in the whole computation of a target algorithm," thus rendering the third attack impractical.

Later, Barenghi et al. [24] (2010) used the same method to recover AES round sub-keys using differential fault analysis (DFA). The approach is independent of the key length and the number of rounds, and requires both fault-free and faulted ciphertexts from the same plaintext. The authors interrogated the same SoC from [23], which executed Linux 2.6 and a software AES implementation based on OpenSSL. After experimental analysis, key recovery could be achieved following 100,000 encryptions with different plaintexts and 2,000,000 encryptions of the same plaintext.

In 2016, Timmers et al. [158] demonstrated two voltage FIAs for privilege escalation on a Xilinx Zynq-7010 SoC (ARM Cortex-A9). Both attacks exploited instruction corruption vulnerabilities with two load instructions (LDR and LDMIA) on the 32-bit ARM architecture (AArch32), which occurred when under-volting the device. The first FIA targeted the BL1 bootloader (see §2.3) to gain code execution privileges within the TEE. It required the BL1 image to be initially overwritten with a malicious payload containing shell-code and relevant pointers; the fault was then precisely injected after shellcode was copied into volatile memory and

<sup>&</sup>lt;sup>4</sup>We note that the target is a single-core, low-frequency (266 MHz) SoC, which can be considered obsolete nowadays.

Figure 8: VoltJockey attack sequence [125].

during the copying of the pointers. On successful occasions, the instruction corruption caused the processor to copy the pointer into its program counter (PC) register, therefore executing the shellcode and transferring control flow to the attacker. The second method used the same approach as an exploit delivery mechanism in situations where the REE and TEE communicate over a shared memory buffer. The fault was injected after loading the shellcode during the world context switch, causing the CPU to load the shellcode pointer into the PC register thereby triggering its execution in the TEE. In total, 10,000 fault attacks on the LDR and LDMIA instructions were conducted. Only a single (0.01%) corruption occurred using LDR, whereas 27 glitches were successful (0.27%) against LDMIA. Neither attack was mounted against TEEs or secure boot processes on an OEM mobile device.

In 2017, Timmers and Mune [156] demonstrated voltage FIAs for Linux-based privilege escalation on an undisclosed ARM Cortex-A9-based SoC. After determining the glitch parameters—the voltage, length, and delay (Figure 7)—the authors targeted the open syscall when an unprivileged application attempted to access physical memory via /dev/mem/. The application was instrumented to trigger the fault during the kernel's access control check, which caused it to be skipped. The second FIA used the instruction corruption attack from [158] to change the CPU PC register to a predetermined address while executing random kernel syscalls, generating system crashes as a proof of concept. The third attack used an FIA to bypass the kernel's security check during the setresuid syscall in order to set an unprivileged application's process ID to root. The success rates of each attack were 0.53% (attack one), 0.63% (two), and 0.41% (three) following 22,118, 12,705 and 18,968 experiments respectively over 17-21 hours.

The NCC Group [117] (2020) published a voltage glitch vulnerability on a MediaTek MT8163V SoC (ARM Cortex-A53). A potential voltage glitch was discovered after the first bootloader is loaded from eMMC into RAM, causing a signature verification check to be skipped. A glitch trigger was implemented on eMMC activity to dynamically insert and load an unauthorised boot component containing code for privileged execution (EL3) with a success rate of 15.21%–23.44%. While not practically demonstrated, the

authors posited that the glitch could be used to load an unauthorised TEE image.

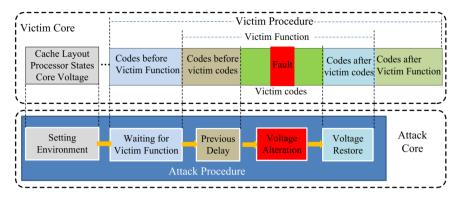

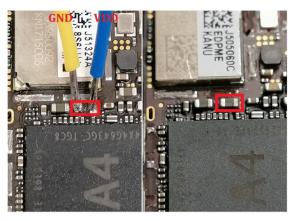

The previous attacks mounted voltage FIAs from external generators, but recent work has shown that dynamic voltage and frequency scaling (DVFS) frameworks can be used for on-SoC fault generation. DVFS regulates the operating frequency and voltage of CPUs for minimising its energy consumption. In 2019, Qiu et al. [125] released the VoltJockey attack on TrustZone-based SoCs, which made use of kernel drivers for controlling the power management IC (PMIC) in software. After establishing root access, the CPU voltage was lowered to the point where cross-core faults were generated on a multi-core system (Figure 8). Because both worlds of execution use the same physical processor, faults could be triggered in the non-secure world for key recovery from the secure world. The authors could induce byte errors during RSA signature verification and AES's eighth round using reference software implementations. The former was used to force the loading of an unsigned TEE application by the TrustZone OS. Proof-of-concept attacks were mounted on a Google Nexus 6 smartphone with a Qualcomm APQ8084AB SoC, with presented rates of 4.6% (RSA verification) and 2.2% (AES key recovery). The code for these attacks, however, have never been released. On non-mobile systems, similar attacks have been used since against Intel SGX on X86-64 platforms [35, 126, 115].

#### 3.2.2. Clock Glitch Attacks

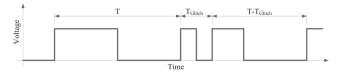

Clock glitch attacks perturb device clock cycles, e.g. introducing additional edges (Figure 9), in order to induce hardware synchronisation issues. This can trigger instruction misses, caused by forcing the execution of an instruction before the CPU has completed the previous one, and data misreads from attempting to read values before the memory has latched out the request. Clock glitches have attracted significant attention against simpler systems [20, 104, 105]. However, at the time of publication, they have found limited application to mobile device SoCs.

An exception is CLKSCREW by Tang et al. [153] (2017), which uses software-controlled power management for crosscore fault generation on TrustZone-enabled SoCs. The attack also exploits DVFS—see Qiu et al. [125] in §3.2.1—

Figure 9: Using an FIA to introduce an additional positive clock edge [85].

for overclocking the CPU to fault secure world operations from the non-secure world. Two attacks are presented: 1), secure world AES key recovery; and 2), corrupting RSA signature verification checks used by the trusted OS prior to loading TAs. CLKSCREW has several prerequisites: kernel access is required to control the power manager, the core clock frequency must be modifiable, interrupts must be disabled, and the target TA must be repeatedly invoked from the non-secure world to decrypt arbitrary ciphertexts. The authors evaluated a Google Nexus 6 using a Qualcomm Kraitbased SoC and a TEE OEM implementation. On average, useful faults were generated at a 5% rate for inducing a one-byte fault to a desired AES round for AES key recovery, and 1.51% for the RSA attack.

Besides CLKSCREW, no other publications have used clock glitches against mobile SoCs to our knowledge. In the recent MCU literature, Korak and Hoefler [85] (2014) used clock FIAs to skip arithmetical (adds), branch (beg and breq), and memory instructions (1dr and str) on a 16-bit AVR ATxmega256 and 32-bit ARM Cortex-M0. They discovered that solely using clock glitches was ineffective on the Cortex-M0, leading to a combined approach of using voltage underfeeding in conjunction with a clock FIA; the ARxmega256 did not require underfeeding. The attacks principally affected the fetch and execute stages of the MCUs' instruction pipelines, which could be induced with high probability (up to 100%). The test hardware was a Xilinx Spartan-6 XC6SLX45 FPGA with a NXP LPC 1114 (ARM Cortex-M0) and ATxmega256A3 extension board. No attacks were presented against security mechanisms or cryptosystems.

In 2014, Blömer et al. [29] presented a clock FIA against an Atmel AVR XMEGA A1 that executed an implementation of pairing-based cryptography (PBC) from the RELIC toolkit [12]. The authors discovered a clock glitch vulnerability that triggered the skipping of a jump instruction (rjmp), which was used for secret key recovery following 4,000 fault attempts (0.025% success rate).

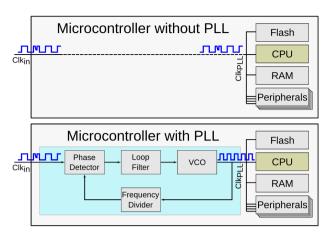

A difficulty of performing clock glitches on modern systems is the prevalence of phase-locked loop (PLL) circuits (Figure 10), which process external clock sources into the system frequency thereby acting as a filter. Traditional FIAs that manipulate external clock frequency do not, therefore, straightforwardly influence the internal clock on modern ICs. In 2019, Selmke et al. [140] were able to successfully attack a PLL-equipped STM32F0308R with an ARM Cortex-M0 CPU. The approach necessitated an extreme clock glitch that effectively overclocked the PLL in order to produce deterministic perturbations in its output frequency. Using this,

Figure 10: A microcontroller with and without a phase-locked loop (PLL) circuit using an external clock input [140].

full key recovery was achieved against a reference software implementation of AES in electronic codebook (ECB) mode. In total, 1,000 faults were injected of which 16.4% were exploitable.

#### 3.2.3. Heating Attacks

Exposing ICs to extreme temperatures has been known for >15 years to generate multi-bit errors in DRAM memory and read/write threshold mismatches in non-volatile memory [82]. Govindavajhala and Appel [66] (2003) presented a proof-of-concept showing that temperature-induced bit errors can lead to security vulnerabilities on a personal computer. A 50W light bulb increased the DRAM working temperature to 100°C, which triggered up to 10 flipped bits per 32-bit word with a 71.4% probability. The authors used this to circumvent the Java type system to expose vulnerabilities in two commercial Java virtual machine (JVM) implementations. In general, heating attacks are among the most destructive of FIAs, leading to long-lasting component/IC damage if the exposure is too high and for too long [25]. As far as we are aware, no heating attacks have been published against mobile device SoCs.

In the MCU literature, Hutter and Schmidt [77] (2013) published heating FIAs on an AVR ATmega162. A low-cost laboratory heating plate heated the MCU to >150°C, beyond its maximum specified temperature limit (125°C). The IC exhibited faults between a 152-158°C window in which RSA-CRT decryptions were executed at 650ms intervals using a reference software implementation over a 70 minute period. This elicited 100 faults of which 31 were exploitable using the Boneh et al. [30] RSA-CRT fault attack to recover one of the prime moduli. In 2014, Korak et al. [86] exposed an AVR ATmega162 to temperatures of up to 100°C to facilitate clock glitches against an 8-bit smart card MCU. They showed that higher temperatures led to higher success rates for inducing erroneous instruction repetitions, replacements, and modifications of their destination registers. Attacks on particular cryptosystems or security mechanisms were not shown, however.

#### 3.2.4. Electromagnetic FI (EMFI)

Another widely studied attack vector is to expose device components to strong electromagnetic pulses. One of the earliest fault models was presented by Quisquater and Samyde [129] (2002) in which EM-induced Eddy currents in the target circuit are captured by its latches, thus generating bit faults. Subsequent fault models have been developed since, such as Raoult et al. [130] (2015) who examined the coupling of a near-field probe to a printed circuit board (PCB) micro-strip line. Generally, electromagnetic FIs (EMFIs) have greater spatial precision than other non-invasive FIAs. High-precision probes connected to EM pulse generators can be used to perturb specific IC regions while shielding other components. EMFIs have attracted significant attention from the research community since their use on smart cards in the early-2000s [129, 104, 105].

EMFIs on Mobile Phone SoCs. To our knowledge, Cui and Housley [38] (2017) presented the first attack on a moblie phone SoC, known as BADFET, which used second-order effects of EMFIs where faults in one component also induced faults in dependent components. A low-cost test-bed (\$300 USD) was used to corrupt the contents of DRAM and NAND flash memory, which triggered a CPU instruction cache fault where bootloader code was loaded. The authors were able to skip into an unreachable code region of the bootloader containing a command line interface (CLI) for debugging purposes. Through this, a separate binary was loaded that exploited an existing vulnerability in the TrustZone SMC implementation (see §2.2.2) for privileged TEE code execution. A Cisco 8861 IP Phone with a Broadcom BCM11123 SoC was used as the DUT, where the attack could be repeated across 72/100 attempts (72%).

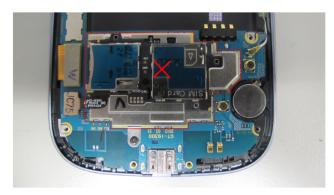

In 2019, Aït El Mehdi [3] presented the first public results on applying EMFIs against a package-on-package (PoP) SoC. The initial research goal was to disable the Android lock-screen's timeout countermeasure to protect against brute force attacks. While this did not succeed, EMFIs could be used against the PoP SoC's upper DRAM package to trigger instruction corruption errors for modifying program control flow. Interestingly, the glitched instructions persisted in the CPU instruction cache as long as it was not replaced. The specific device and SoC models are redacted, however.

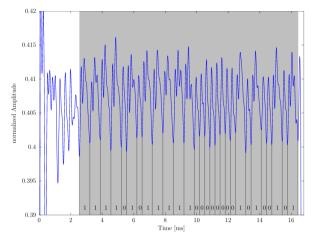

Gaine et al. [48] (2020) presented a privilege escalation attack on a 64-bit (non-PoP) SoC with four ARM Cortex-A53 CPUs (1.2GHz) on a mobile development board, which ran version 4.14 of the Linux kernel from the Yocto Project's Sumo release. EM pulses were fired using an injection probe, shown in Figure 11, on an XYZ motorised stage. Only one CPU on the DUT was sensitive to EMFIs after characterising the temporal and spatial requirements using a test program. An instruction skip vulnerability was identified with a conditional branch instruction (cbz) in the string comparison (strcmp) C function. This was exploited to bypass the password comparison check used by the substitute user command (su) using a software trigger in the 1ibpam kernel module. Without DVFS enabled, EMFIs were generated every

Figure 11: EMFI probe used by Gaine et al. [48].

two minutes for the same CPU with a fixed frequency and probe position (overall success rate of 2%). With DVFS enabled, 21 of 6000 FIs were useful (0.35%), equivalent to one success for every 300 attempts (15 minutes).

In other work, Trouchkine et al. [160] (2019) detailed micro-architectural and instruction-level software methods for expediting EMFI characterisation on modern SoCs. Using these, the authors were able to establish the location of useful faults on ARM and Intel CPUs; that is, whether they perturbed data in CPU registers, the pipeline, MMU, caches or external memory. Experimental results showed that faults on CPU registers, the CPU pipeline, or memory could be identified on a Broadcom BCM2837 SoC (ARM Cortex-A53 at 1.2GHz) and an undisclosed Intel Core i3 CPU with 95% and 80% accuracy respectively.

*EMFIs on MCUs.* Dehbaoui et al. [39] (2013) mounted an EMFI-based key recovery attack on a reference software AES implementation on a 32-bit ARM Cortex-M3 MCU (24MHz). The work targeted the AES round counter at the ninth and tenth rounds to induce an additional round of execution with high success (up to 100%). This enabled feasible cryptanalysis with which the encryption key could be recovered using two pairs of correct and faulty ciphertexts.

Menu et al. [107] (2019) presented data corruption EM-FIs against the transfer bus from flash memory to the internal buffer of an Atmel SAM3X8E MCU (ARM Cortex-M3). Without disturbing code execution, the authors could reset data items of length 0–128 bits with byte-level precision by targeting the pre-fetch mechanism using an EM generator with a square voltage pulse (200V maximum amplitude), a 6ns minimum width and a 2ns transition time. Four components were shown to be vulnerable: the flash memory, the 128-bit pre-fetch buffer, bus interfaces, and the register file. A reference software AES implementation was then interrogated using a key is stored in flash memory. For the first attack, the EMFI could reset the value of the entire key as it was fetched from memory (100% repeatability). The second applied the DFA from Biham and Shamir [28], which assumes the attacker can collect ciphertexts of known plaintexts while incrementally resetting one bit of the secret key until a zeroed key is reached. This was used to reduce the potential key-space of a 128-bit AES key to  $16 \times 2^8$ , which could be brute-forced. The final investigation presented a fault attack that uses an EMFI to induce a persistent fault in AES S-box look-up elements. Encryptions using the S-

box produced faulty ciphertexts if the corrupted entry was accessed, where it was shown that the effective key entropy reduced to 32-bits when four such S-box elements were used.

Similar to the aforementioned work in [160], Majéric et al. [101] (2016) showed how EM side-channels could expedite EMFI parameter setting against an AES implementation aboard the security co-processor of an IoT SoC. The EMFI location was set using EM emissions corresponding to particular Hamming weights during intermediate AES operations. The ninth AES round was successfully faulted at a rate of 0.03% after which faulty ciphertexts could be used for key recovery using the Piret and Quisquater [123] DFA. Unfortunately, the identities of the SoC and its co-processor are not disclosed.

Liao and Gebotys [94] (2019) combined EMFIs and overclocking for disrupting the pre-fetch stage of an 8-bit MCU (Microchip PIC16F687). After performing backside decapsulation, the authors caused instruction replacement errors by inducing bit-level opcode faults within several test programs. An exclusive-or (xorwf) and move-literal (movlw) instruction were particularly vulnerable, which could be replaced with alternatives—e.g. goto, inclusive-or (iorwf) and bit-clear (bcf)—with a frequency of 1.8%–98.7%. A key recovery attack was then shown against a reference AES software implementation requiring 222 EM pulses and 5.3 plaintexts on average. It is mentioned that goto instruction replacement errors may be used bypass boot-time authentication checks, but a concrete attack was not presented.

Other than examining cryptographic implementations, several works have applied EMFIs to trigger general instruction and data corruption faults. Moro et al. [113] (2013) discovered instruction and data corruption vulnerabilities by targeting the data and instruction buses on an ARM Cortex-M3. EMFIs were used to: 1), modify the values of 1dr instructions to alter data flow; 2), generate hardware exceptions to modify control flow; 3), replace memory store (str) instructions; and 4), modify CPU registers. Experimental results explored the effect of EMFI pulse amplitudes on the number and relative frequency of bit faults on data fetches from flash memory.

In a similar vein, Riviere et al. [131] (2015) interrogated the instruction cache of an ARM Cortex-M4 by targeting an EMFI during the updating of the CPU's pre-fetch queue buffer with 96% success. Using custom assembly programs, four instructions could be skipped while the subsequent four instruction could be replayed. No security-critical systems were compromised, but the authors posit that the fault model could be used against CRT-based RSA, AES, and for privilege escalation on ARMv7-M targets.

Elmohr et al. [42] (2020) discovered an EMFI-based instruction corruption fault during the execution stage of load (1dr) instructions on an NXP LPC1114 (ARM Cortex-M0). Using a test program, the errors appeared when a branch (bne) instruction was fetched at the same time. EMFIs were used to fault two, three, four and instructions at the same time with a frequency of 31%, 13%, 12% and 12% respectively. Like [94], the MCU must be decapsulated.

#### 4. Side-channel Attacks

Rather than inducing abnormal conditions into electronic components, physical side-channel attacks exploit observable phenomena emitted during their operation. This can reveal key material and other data if the phenomenon can be reliably associated with data or operations under execution. The origin of these attacks date back to the disclosure of the NSA TEMPEST programme [47], which described how vulnerable cryptographic implementations can produce certain electromagnetic characteristics depending on the input key and data. The area has since attracted tremendous attention from the research community, with associated vulnerabilities still plaguing today's systems [34, 61, 170, 171, 175, 103].

A standard SCA testing setup was shown in Figure 6. Here, an oscilloscope acquires measurements (traces) of the chosen phenomenon, e.g. EM emissions, using probes attached to sensitive DUT regions, which are then analysed by the investigator on an external computer. Like FIAs, the target may be instrumented with hardware or software triggers to collect precise measurements of particular operations of interest. In existing literature, two SCA approaches have been widely utilised:

- **Power analysis**: Leverages time-series differences in the target's power consumption during sensitive procedures [61, 122, 137, 74, 120, 114].

- EM analysis: Exploits electromagnetic radiation signatures produced by the target [1, 81, 116, 111, 19, 62, 99, 26, 33, 34, 4, 171].

Beyond these approaches, two alternative methods have also been explored in the wider literature, albeit with limited applicability to mobile systems:

- Acoustic cryptanalysis: Capitalises on properties of sound waves, such as the emission of certain frequencies and their change over time [50].

- **Temperature analysis**: Uses differences in the target's temperature during its operation [77].

We observe that only EM-based attacks have been used extensively on mobile phone SoCs. The others have been employed predominantly against simpler SoCs and MCUs, which we discuss as supplementary information.

## 4.1. Power Analysis

Power analysis exploits device power consumption measurements to discover information about sensitive code and data under execution. Modern ICs contain millions of transistors that act as voltage switches. These are continually switched on and off during execution, causing voltage fluctuations that can be measured using commercially available testing equipment. The resulting measurements are analysed, whether through direct inspection or using statistical analysis, for inferring information about cryptographic keys and individual instructions under execution [114, 104, 137].

Interestingly, very few power analysis attacks have been conducted on mobile devices. In one exception, Genkin et al. [49] (2016) used a power tap on an Apple iPhone 4 USB charging port, requiring a USB pass-through adapter with a  $0.33\Omega$  resistor placed in series with the ground line. The authors connected the phone to a battery pack via the adapter and collected measurements using voltage changes over the resistor. Through analysis, five ECDSA scalar-by-point multiplication operations (using the same point and four different scalar values) could be distinguished using OpenSSL's NIST P-521 implementation. Details were not presented regarding its effectiveness for full recovery or its transferability to other devices. The second instance we are aware of, published by Lisovets et al. [97] (2021), is an additional investigation of an EM-based side-channel attack on an iPhone 4, which we discuss in §4.2.

In general, power analysis attacks on mobile SoCs face a myriad of challenges. Firstly, their density renders it difficult to capture reliable measurements, with varying power planes, voltage regulators, and landside decoupling capacitors compared to MCUs. Modifying mobile SoCs to access reliable power sources is not a trivial endeavour and risks serious damage to the device. Secondly, attacks must account for potential interference from multi-core CPUs and multitasking OSs; the power consumption of specific operations of interest must be distinguished from aggregate measurements of the entire system. Furthermore, modern PoP designs require researchers to account for the power consumption of multiple packages in addition to the aforementioned complexities. All of these aspects dramatically complicate power analysis attacks on mobile devices.

In the remainder of this section, we cover recent research targeting embedded systems, e.g. IoT SoCs, which may provide a gateway for analysing mobile SoCs in future work.

## 4.1.1. Key Recovery

Most key recovery attacks employ a common set of techniques for analysing power traces. Simple power analysis (SPA) involves directly inspecting traces to deduce secret information when measurements can be mapped to certain data properties, e.g. distinct voltages corresponding to individual key bits. Differential power analysis (DPA), an advanced technique presented by Kocher et al. [83], uses correlations between the Hamming weight of intermediate cryptographic operations and measurement traces to determine the likelihood of particular key bytes. Template analysis involves collecting a set of traces and labelling them with the corresponding cryptographic operation. Freshly measured traces are then classified by mapping it to its closest matching template from the set.

Over the last 20 years, SPAs, DPAs, and template analyses have been studied in great detail on smart cards, FPGAs and embedded systems [104, 103, 44, 112]. Recent work has explored machine and deep learning methods for providing greater discriminative power using fewer traces over existing statistical methods. Heuser and Zohner [74] (2012) explored the use of support vector machines (SVMs) for this purpose.

Power traces were collected from an 8-bit AVR ATMega-256-1 MCU (8MHz) using a reference AES software implementation. The AES S-box was used as the profiling target in which the SVM predicted the Hamming weight from the measurement trace. The authors were able to recover the key using 20 traces in low-noise and up to 60 traces in high-noise environments. Beyond power analysis, traditional machine learning has also been used for side-channel analysis in other problem spaces, such as recovering information about physically unclonable functions (PUFs). We refer to Hettwer et al. [73] for a detailed survey of this work.

Deep learning (DL) methods—neural networks with multiple hidden layers—are also being increasingly used in stateof-the-art attacks, which can capture complex, non-linear interactions between power traces and target cryptographic operations. Maghrebi et al. [100] (2016) presented some of the first results applied to AES key recovery by targeting AES's first-round S-box. The first attack focussed on an unprotected FPGA-based AES implementation, showing that key recovery can be achieved with 200 traces using a convolutional neural network (CNN). In the second, an unprotected reference software AES implementation was examined on a Chipwhisperer—a development board for sidechannel analysis with an AVR ATMega328P MCU. Using an autoencoder neural network, the first four AES key bytes could be recovered with 20 traces. In the final experiment, a masked AES software implementation on the Chipwhisperer was investigated; in the best case, an autoencoder and CNN could recover the secret key using 500 and 1,000 traces respectively.

The application of CNNs was also explored by Picek et al. [122] alongside simpler machine learning methods. Similarly, they used the Hamming weight model at first-round AES S-box operations. Protected AES implementations were examined using the DPAContestV2 [36] dataset, comprising 50,000 traces from an Atmel AVR MCU. A 91.2% test accuracy was achieved for correct Hamming weight classification using a CNN. Simpler methods—XGBoost, Naïve Bayes, and Random Forests—were also used effectively, where the key was recovered in under 10 traces. Wang [170] (2019) conducted similar work using CNNs for key recovery against two AVR ATXmega128D4 MCUs with a 128-bit AES-ECB reference software implementation. Interestingly, the average number of required traces differed significantly between the boards (160 and 400 traces per MCU).

As an alternative to tapping into current-carrying wires, Schmidt et al. [137] (2010) used miniscule power fluctuations measured at exposed I/O pins. The authors targeted five devices running a reference 128-bit AES software implementation without side-channel countermeasures: an 8-bit Atmel ATMega163 and AT89S2853 MCU, an NXP LP2148 MCU with a 32-bit ARM ARM7TDMI-S CPU, a Virtex-II Pro XC2VP7 FPGA, and an ASIC. Plaintexts were over a serial interface to the targets and, during encryption, an oscilloscope recorded the voltage variations at an exposed I/O pin. DPAs were reportedly successful on all devices, but the required number of traces were not given.

**Figure 12:** Power consumption of the NOP, MOV, ADD, and SUB ATMega163 instructions [114].

Recently, Gnad et al. [61] (2019) showed that crosstalk in analog signals from adjacent on-SoC digital components could be exploited for key recovery. The threat model is an on-device malicious program that wishes to learn information about secret data used by a parallel program on another CPU core. The authors used the effect of noise fluctuations generated by digital subsystems that were modulated into (on-SoC) analog-to-digial (ADC) converter signals. A spy program accessed ADC measurements while the victim used a software AES implementation from mbedTLS to execute single 128-bit AES encryptions of plaintext messages. Using a range of IoT SoCs—a ESP32-devkitC, an STM32L475 IoT Node, and an STM32F407VG Discovery—correlation analysis attacks were mounted by targeting the final AES round and analysing 10 million ADC noise traces.

#### 4.1.2. Instruction Profiling on MCUs

Another less-studied use of power analysis is to identify individual instructions in use, which has applications to reverse engineering and detecting unauthorised program execution. In this area, Msgna et al. [114] (2014) analysed power consumption traces from an Atmel ATMega163 using the voltage drop across a shunt resistor on the MCU. 11 instructions were profiled—Figure 12 shows a sample trace of four ATMega163 instructions—using template analysis after applying dimensionality reduction as a feature extraction technique. The work used two statistical models—k-Nearest Neighbour (kNN) and a multi-variate Gaussian probability distribution function—to classify instructions from their associated traces, achieving a 66.78-100% recognition accuracy depending on the method. In 2018, Park et al. [120] profiled a much larger set of instructions on an AVR AT-Mega328P MCU (112 in total). A classification model was developed based on quadratic discriminant analysis, which was trained on 2,500 power traces per instruction, achieving a recognition accuracy of 99.03%.

## 4.2. Electromagnetic Emission (EM) Analysis

Using EM emissions to compromise vulnerable security systems can be dated back to 1943 when a Bell Telephone engineer discovered oscilloscope perturbations while using an encrypted teletype, the Bell 131-B2. The partial declassification of the NSA's TEMPEST programme in 1972 subsequently documented more elaborate efforts to subvert electronic systems in this way, as well as identifying potential countermeasures [173, 47]. These side-effects arise from charge movements through transistor gates, wires etc., which emit electromagnetic radiation that can be measured using

Figure 13: Experimental setup used by Aboulkassimi et al. [1].

non-invasive means.<sup>5</sup> EM analysis has been widely used to break security and cryptographic implementations on systems from simple smart cards to high-frequency SoCs [83, 68, 118, 108, 109]. This section surveys state-of-the-art EM-based SCAs, which, unlike power analysis, has been employed extensively against mobile devices.

EM SCAs on Mobile Phone SoCs. To our knowledge, Aboulkassimi et al. [1] (2011) published the first EM-based SCA on a mobile phone, targeting reference AES software implementations on the Java Platform, Micro Edition (Java ME). Measurements were triggered using the device's microSD card interface, which were acquired using a commercially available EM probe and oscilloscope (see Figure 13). The authors presented methods to overcome temporal distortions in EM traces from just-in-time (JIT) compilation and garbage collection used by the Java Virtual Machine (JVM). Two methods—a spectral density-based approach (SDA) and a template-based resynchronisation approach (TRA)—were proposed to statistically navigate these issues. Using the second approach, one AES key byte could be recovered in an hour with 250 traces from an undisclosed device with a 32bit RISC processor (370MHz). Like [23], however, this platform can be considered obsolete nowadays.

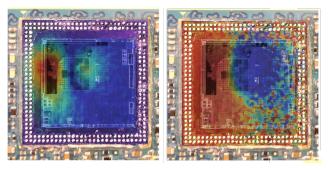

In 2012, Kenworthy and Rohatgi [81] reported ECC-, RSA- and AES-based key recovery attacks on three undisclosed mobile devices. The first—a "4G LTE smart phone from a major manufacturer"—performed RSA-CRT encryptions (2048-bits) using a self-written square-and-multiply implementation. From a single trace, the secret exponent could be recovered using a Yagi antenna, magnetic probe, ICOM 7000 receiver, and an Ettus Research USRP digitizer costing \$1000 (USD) at the time. The second device, "a mobile PDA," performed elliptic curve point multiplication over P-571 using a self-written double-and-sometimes-add implementation. The authors achieved full key recovery using a single trace from an EM probe located three meters (10 feet) from the device. The third, "another mobile phone from a major mobile manufacturer," used an OEM cryptographic

<sup>&</sup>lt;sup>5</sup>While EM-based SCAs are usually non-invasive, more reliable traces may be collected after invasive intervention, e.g. IC decapsulation, to eliminate unwanted attenuation.

**Figure 14:** Device under test used by Goller and Sigl [62]. The red cross indicates the optimal EM probe position.

library to perform 128-bit AES-CBC encryption on a 200kB data buffer. In this attack, traces corresponding to 12,500 individual AES block operations were required to perform DPA-based key recovery. For all targets, the SoCs were not disclosed nor were the use of any triggers.

Nakano et al. [116] (2014) presented EM-based key recovery attacks against ECC and RSA implementations from Android's Java Cryptography Extension (JCE) library on an undisclosed smartphone (832MHz clock frequency). The RSA implementation used a square-and-multiply approach, which was already known to be vulnerable to side-channel analysis. Like [81], identifiable ECC double-and-multiply operations were also exploited. Both methods used simple power analysis at the 10 MHz and 20 MHz frequencies for key recovery using a single trace. The precise nature in which triggers were implemented are not disclosed.

In 2015, Balasch et al. [19] presented EM-based DPA attacks against a Texas Instruments AM3358 Sitara SoC on a Beaglebone Black single-board computer (SBC) with an ARM Cortex-A8 (1GHz) and a Debian 7-based Linux distribution (kernel v3.8.13-bone47). The authors targeted an unprotected 128-bit AES software implementation and a bit-sliced version from Könighofer [84] (2008) designed to resist side-channel analysis. After analysis, 1.2 million traces were needed for key recovery using the bit-sliced implementation and a first-order DPA, while a second-order DPA was possible using 400,000 traces. In contrast, only 10,000 traces were required for the unprotected algorithm.

Goller and Sigl [62] (2015) attacked a reference software RSA implementation using the square-and-multiply method on five unnamed smartphones. The device's shielding plate was removed to reduce EM attentuation; a software-defined radio, a probe and a high-gain amplifier at a capacitor near the main CPU were then used for the measurement acquisition. Using simple power analysis, the waveforms were strongly correlated with individual bits of the secret key (Figure 15). 276 traces were required for full key recovery with high confidence (0.999 correlation) and the shielding plate installed, while 170 were needed without the shielding.

Figure 15: Average of 1063 RSA EM traces. Grey regions show the key bits recovered by Goller and Sigl [62].

Also using a BeagleBone Black SBC, Longo et al. [99] (2015) conducted EM DPAs against two AES implementations: 1), software-based 128-bit AES in CBC mode taken from OpenSSL; and 2), a 256-bit AES implementation on the SoC's cryptographic co-processor. For the software implementation, 20,000 traces produced the correct key hypothesis, while the co-processor required 500,000 sets of 1,000 averaged traces (500 million traces in total). Notably, they state that the latter may be useful against full-disk encryption implementation. While no exploits were presented to this end, it is one of the few papers to successfully attack a physical cryptographic co-processor, although no proof-of-concept code has been publicly released.